Pass EMC Testing Without Slowing Down Development

Get expert EMC reviews in 3 business days when you need fast guidance

or full EMC project delivery when you need to pass the lab on the first try.

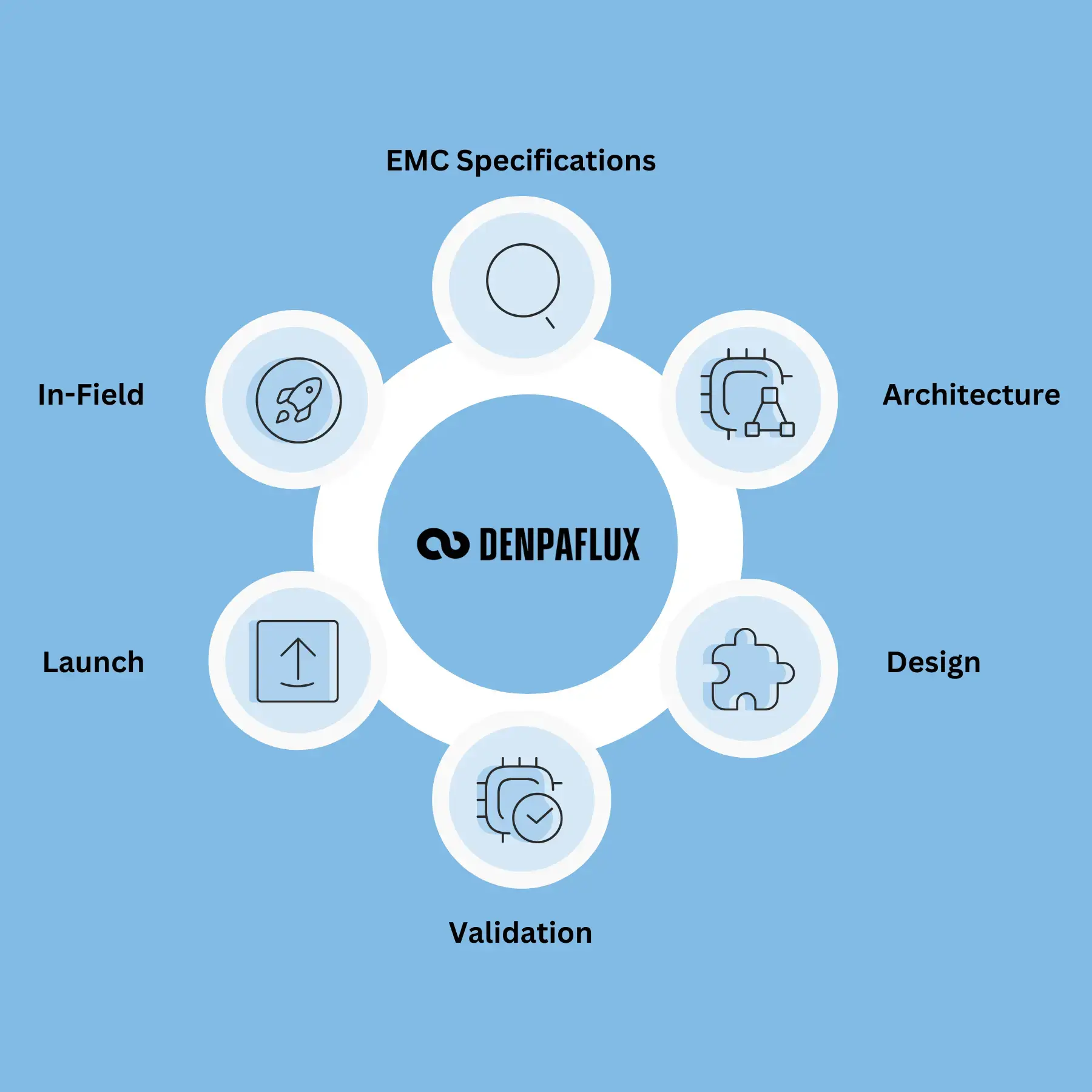

Experience DENPAFLUX Way to Solve your EMC Challenges

See how DENPAFLUX helps electronics design teams to eradicate EMC issues faster & easier by providing iterative consultation as of the early product development cycle with our AI-infused EMC service.

The Problem

Traditional EMC Is Reactive, Fragmented, and Late

Disconnected workflows, late-stage testing, and unclear ownership turn EMC into a blocker: slowing development, increasing costs, and putting product launches at risk.

Development Gaps

EMC Treated as a Validation Step, Not a Design Constraint

Architectures, layouts, and component choices move fast, while EMC considerations lag behind. Issues are discovered only when changes are expensive and schedules are locked.

Process Breakdowns

No Clear Ownership From Design to Certification

Responsibility is fragmented across engineering, compliance, and external labs. Standards are interpreted late, decisions happen in silos, and teams react to failures instead of managing compliance end-to-end.

EMC Compliance Delays

Unclear Readiness Delays Product Launches

Regional requirements and certification scope are often defined too late. Gaps appear only after lab bookings—leading to failed tests, retesting costs, and delayed market entry.

The Solution

One EMC Partner for Every Stage of Hardware Development

From early EMC design reviews to EMC lab testing, compliance, and in-field issues, DENPAFLUX provides reliable EMC support across the full hardware development lifecycle.

Fast, Actionable EMC Services When Decisions Matter

Receive clear, prioritized EMC and EMI analysis with detailed solutions within days, so design, layout, and architecture decisions move forward without waiting weeks for consultant feedback.

EMC Expertise Matched to Your Product and Industry

DENPAFLUX assigns EMC specialists based on your technology—power electronics, RF, industrial, or consumer, ensuring guidance matches real-world product constraints and standards.

Predictable Paths to EMC Compliance

EM;C Standards, scope, and test strategy are defined upfront—reducing failed tests, rework, and last-minute surprises.

Enterprise Security for Sensitive Product Data

Sharing schematics, PCB files, and EMC data requires trust. DENPAFLUX protects your IP with enterprise-grade security, so you can focus on passing EMC compliance, not worrying about data leaks.

Enterprise-Grade Encryption

All files encrypted in transit and at rest. Hosted on secure German servers.

Your IP. Your Ownership.

Design data stays your intellectual property. We never share or sell your files.

GDPR Compliant

Full European data protection. Secure deletion available on request.

What engineering teams say about our EMC Services

Thanks to DENPAFLUX, we were able to identify and fix potential EMC issues early in the design process, allowing our engineers to fast-track iteration and fewer re-spins on designs which saved us a lot of time and money down the road.

One of the biggest benefits of working with DENPAFLUX was their easy-to-understand and concrete mentions in the report. EMC recommendation reports were classified by severity, making it easy for us to understand the findings and take action on them. We couldn't be happier with the results.

DENPAFLUX prompted our team of design engineers to thoroughly revisit and analyse the specific design elements in question, resulting in enhanced rationale for our design decisions They empowered us to achieve optimal solutions and strengthen our design process!

To ensure that we don’t lose months

to a redesign we use DENPAFLUX to check for possible EMC problems. Having another AI-powered pair of eyes meticulously checking every circuit will always be beneficial. The knowledge and best practice techniques learned from the detailed reports also help us in avoiding certain error sources from the get-go.

HOW IT WORKS

Get EMC Support in Hours, Not Weeks

Book a kickoff meeting

A quick conversation with our EMC expert to scope our project and set up your secure workspace.

Upload your design data

From early architecture to final validation - share your files and your expert begins the review within hours.

Review EMC Findings Together

Receive your EMC report within 3 business days. Then walk through recommendations with our expert to prioritise fixes.

Worried about IP rights ?

Need an NDA Before We Talk?

No problem. Sign our digital NDA in under 60 seconds & then share your product details with confidence.

Your EMC Expert Team, Ready When You Need Them

DENPAFLUX gives hardware teams direct access to experienced EMC engineers. Once you start, a dedicated expert is assigned to your project, no re-explaining your product every call. No hiring. No hourly billing.

0

+0

+0

+0

+Talk through your EMC challenge

A short 30-minutes conversation (non-binding) to understand where your project stands and what’s blocking progress.

Customer Success Story:

How Alfen Built EMC Expertise While Accelerating Hardware Development?

Discover how DENPAFLUX helped Alfen maintain EMC design quality while increasing hardware development velocity.

EMC Support at Every Stage, Not Just When Things Fail

Most teams bring in EMC support after a failed test.

DENPAFLUX helps you avoid that moment entirely - with reliable EMC expertise whenever challenges arise.

What standards actually apply to us?

We identify applicable CE, FCC, RED, and regional EMC requirements early — so your team designs with the right compliance targets from the start.

Is our system architecture EMC-safe?

Grounding, shielding, power distribution, and connector strategy reviewed early — before board spins lock in costly mistakes.

Will this schematic and layout pass?

Decoupling, filtering, stack-up, and routing reviewed and annotated with clear, prioritized recommendations your engineers can act on.

Are we ready for the EMC Test lab?

Test plan review, pre-compliance risk assessment, and lab coordination — so there are no surprises on test day.

We need to pass the EMC Test, now!

Interference issues in the field? We diagnose EMC-related failures, assess component and firmware impact, and help get your product back on track.

"Customers Are Complaining. We Need Answers, Fast.

Product underperforming? Interference issues in the field? We diagnose EMC-related failures, assess component or firmware impact, and get your product back on track.

Built for Industries Where EMC Compliance Is Non-Negotiable

Hardware teams in regulated and high-reliability sectors trust DENPAFLUX to pass EMC testing in first attempt

Medical Device EMC

Consumer Electronics & IoT

RF & Wireless Products

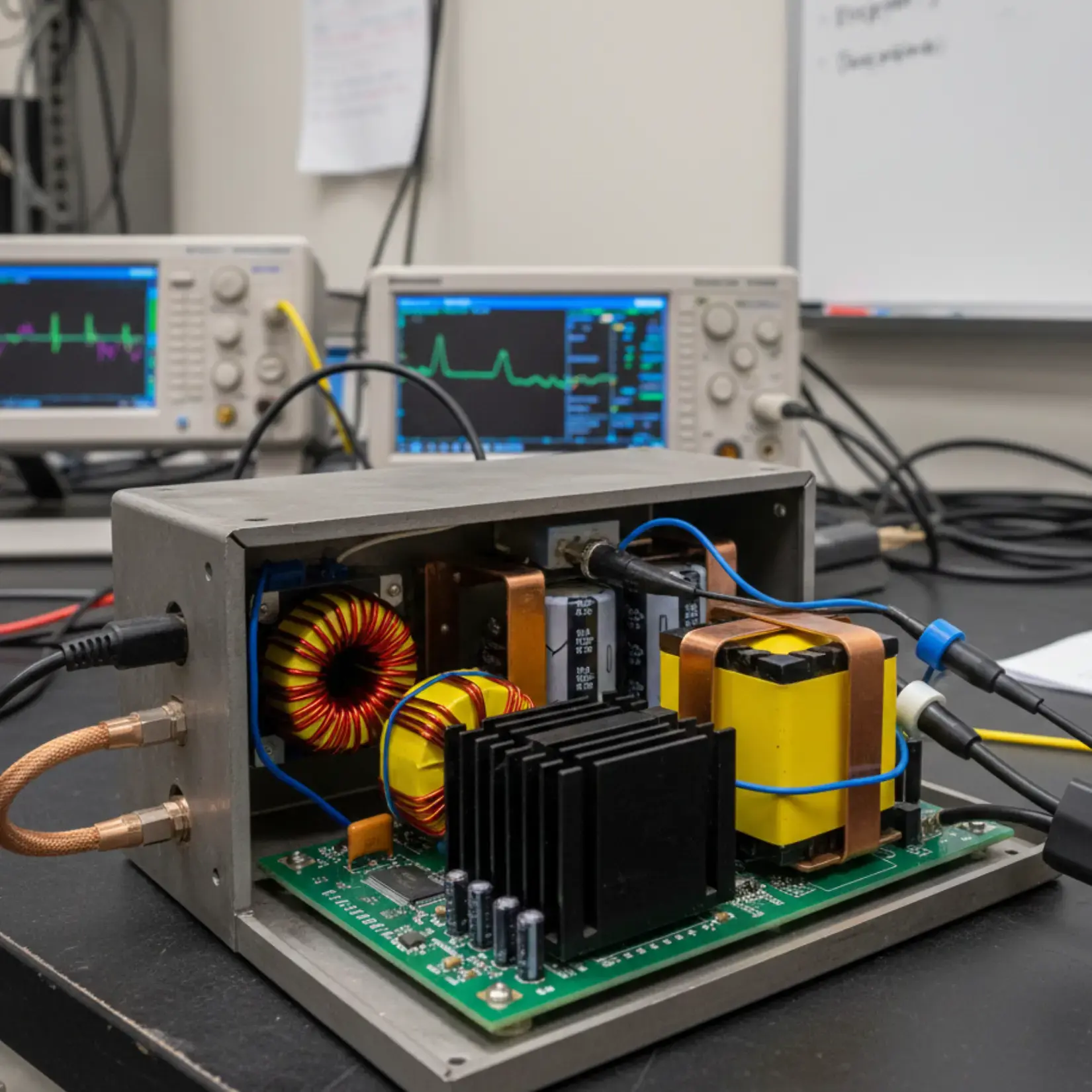

Power Electronics

Industrial Equipment

Aerospace & Space Tech

EMC Expertise On-Demand

Full EMC Project Delivery

What's included

Frequently Asked Questions About DENPAFLUX

Q1: How does working with DENPAFLUX work?

It starts with a short kickoff call to understand your project and EMC challenges. Once scoped & quote is signed, we set up your secure workspace on the DENPAFLUX platform. You upload your design files schematics, PCB layouts, BOMs, or whatever stage you're at and your dedicated EMC expert begins the review. You'll receive your EMC report within 3 business days, then walk through findings together to prioritise fixes.

Q2: What's the difference between EMC Guard and EMC Shield?

EMC Guard is on-demand EMC expertise — you get a dedicated expert, unlimited reviews, and 3-day turnaround. Your team implements the recommendations. EMC Shield is full EMC project delivery — we assign a team of experts, manage your timeline, handle lab testing, and guarantee you pass EMC compliance.* Choose Guard if you have internal capacity. Choose Shield if you want EMC handled end-to-end.

*Guarantee applies when DENPAFLUX recommendations are followed.

Q3. What file formats do you accept?

We accept over 100 file formats including PDF, ODB++, Gerber, ZIP, STEP, and most major EDA tool exports (Altium, KiCad, Eagle, OrCAD, etc.). Whatever stage your hardware development is at from early specs to final validation - we can work with your files.

Meet Our EMC Experts Ready to Solve Your Design Challenges

With decades of combined experience across industries, our EMC specialists provide hands-on expertise from concept to certification. We've helped hundreds of companies overcome complex EMC challenges and build better products

European Market

UK Market

USA & Canada Market